- Las CPU han pasado de integrados simples como el Intel 4004 a complejas arquitecturas multinúcleo con miles de millones de transistores y caches jerarquizadas.

- La miniaturización y el cambio a diseños con chiplets, junto a la rivalidad Intel–AMD, han impulsado saltos enormes en rendimiento y eficiencia energética.

- El presente se centra en núcleos híbridos, GPU integradas y NPUs para IA, mientras el sector se acerca al límite físico del escalado de transistores.

Si miramos atrás unas cuantas décadas, cuesta hacerse a la idea de hasta qué punto ha cambiado nuestra vida gracias a los procesadores. De llamar al timbre del vecino o usar el teléfono fijo para quedar, hemos pasado a vivir rodeados de ordenadores, portátiles, móviles, consolas y dispositivos conectados que damos por hecho… y todos tienen un corazón común: la CPU.

Desde aquel humilde Intel 4004 hasta los actuales chips híbridos con núcleos de potencia, eficiencia y aceleradores de IA, el camino ha sido brutal. La historia de las CPU es la historia de cómo hemos pasado de máquinas del tamaño de una habitación con tubos de vacío a microprocesadores con miles de millones de transistores en un trozo diminuto de silicio, y de cómo estamos chocando ya con límites físicos que obligan a replantearse el futuro.

De los primeros microprocesadores al nacimiento del PC

Antes de que el PC existiera como tal, Intel ya estaba experimentando con integrar una CPU completa en un único chip. En aquellos años la compañía vivía principalmente de vender memoria DRAM y SRAM a fabricantes de miniordenadores, y los procesadores eran casi un “side project”.

El primer gran hito fue el Intel 4004. Diseñado a principios de los 70 por Federico Faggin, Ted Hoff y Stanley Mazor para la firma japonesa Busicom, fue una CPU de 4 bits completa en un solo chip cuando lo normal era tener la lógica repartida en varios integrados. Tenía una frecuencia de unos 740 kHz y apenas unos miles de transistores, pero abrió la puerta a que una empresa relativamente pequeña como Intel demostrara que podía crear un procesador generalista integrado.

A partir de ahí llegó el Intel 8008, otra CPU temprana de 8 bits, ligada originalmente a una terminal inteligente de Datapoint. El proyecto comercial no terminó bien, pero sirvió de base para seguir aprendiendo. Intel no estaba satisfecha con las limitaciones del 8008, así que decidió dar un salto con el Intel 8080, también de 8 bits pero mucho más capaz: dirección de hasta 64 KB de RAM, más puertos de E/S, nuevas instrucciones y frecuencias de hasta 2 MHz.

El 8080 acabó siendo el cerebro del Altair 8800, una de las primeras máquinas que hoy identificamos como ordenador personal, y dio pie a toda una generación de sistemas S‑100 y al sistema operativo CP/M. Sin embargo, la aparición del Zilog Z80, obra del propio Faggin ya fuera de Intel, puso a la compañía en aprietos en ese mercado inicial, al ofrecer una versión mejorada y muy popular para micros como Spectrum, MSX o Amstrad CPC con un rendimiento y versatilidad superiores al 8080.

Con esta experiencia a la espalda, Intel diseñó el 8086, la primera CPU con la hoy omnipresente ISA x86, pensada inicialmente como un proyecto menor frente a otros diseños más ambiciosos como el iAPX 432. El 8086 introducía una arquitectura de 16 bits, pero su nuevo conjunto de instrucciones no era compatible a nivel binario con el ecosistema CP/M, y en un principio fue un chasco comercial. Nadie imaginaba que ese supuesto fracaso acabaría cimentando el estándar del PC.

IBM PC, x86 y el despegue de Intel (y AMD)

En 1981 IBM lanza su PC, no inventando el ordenador personal, pero sí estandarizando una plataforma abierta sobre hardware ya existente. Para la CPU valoraron varias opciones, incluido el Motorola 68000, pero finalmente se decantaron por el Intel 8088, una variante del 8086 con bus de datos de 8 bits que simplificaba el diseño de placas y controladores.

El gran detalle estratégico fue que IBM exigió un segundo proveedor de CPU por seguridad de suministro, y ahí entra en escena AMD como clonador autorizado de x86. De la noche a la mañana, un diseño que parecía condenado al olvido se convierte en el centro de la industria, y con él la ISA x86 empieza a extenderse como estándar de facto.

El 8088/8086 ofrecía una ALU de 16 bits y direccionamiento de 20 bits, permitiendo llegar a 1 MB de memoria, todo un salto respecto al 8080. A partir de ahí llegarían generaciones clave: el 80286, con un IPC más del doble que el 8086, buses internos mejorados, nueva unidad de gestión de memoria (MMU) basada en segmentación y una larga vida comercial en PCs de negocios a lo largo de los 80.

Después aparece el 80386, que lleva x86 a los 32 bits reales aprovechando parte de la experiencia del iAPX 432 pero manteniendo compatibilidad hacia atrás con los registros extendidos. Introduce paginación, multitarea y un pipeline segmentado, haciendo posible sistemas operativos de escritorio verdaderamente multitarea como Windows “serio” a partir de la versión 3, así como la aparición de Linux y el auge definitivo del PC frente a otras plataformas.

El 80486 da otro empujón notable al rendimiento: integra por primera vez la FPU dentro del mismo chip, añade cachés L1 separadas para datos e instrucciones, alarga el pipeline hasta cinco etapas y consigue frecuencias de hasta 100 MHz. A nivel competitivo, supone el golpe definitivo a la línea Motorola 68k y acelera el movimiento de Apple hacia PowerPC, mientras que para Intel reafirma su dominio en escritorio gracias a un aumento extraordinario del IPC respecto al 386.

Pentium, P6 y la consolidación de las CPU modernas

Con el salto a Pentium, Intel introduce la primera CPU x86 superescalar masiva, capaz de ejecutar dos instrucciones en paralelo, lo que supone un incremento de alrededor del 40 % en IPC frente al 486. El posterior Pentium MMX añade instrucciones SIMD para acelerar multimedia, aunque su vida comercial se solapa rápidamente con la llegada del Pentium II.

El verdadero cambio profundo de los 90 viene con la microarquitectura P6, estrenada en el Pentium Pro y luego usada en Pentium II y Pentium III. P6 introduce de lleno la ejecución fuera de orden (OoO), la especulación y pipelines mucho más largos, además de caché L2 integrada o dentro del encapsulado, adelantando muchas de las técnicas asociadas a las CPUs RISC de estaciones de trabajo. Con ello, Intel consigue cerrar filas frente a las arquitecturas RISC dedicadas y refuerza la idea de que x86, bien implementado internamente, puede competir en rendimiento bruto con casi cualquier ISA.

Mientras tanto, AMD avanza también con sus propias arquitecturas: el AMD K6 se convierte en la primera CPU que le da guerra de verdad a Intel en el mercado doméstico, priorizando una buena relación rendimiento/precio y apuntalando la imagen de AMD como alternativa seria. A nivel de 64 bits, AMD será quien dé el salto decisivo con la arquitectura AMD64, que extiende x86 a 64 bits manteniendo la compatibilidad con 32 bits, movimiento que el resto de la industria terminará adoptando por completo.

El Pentium 4 y su arquitectura NetBurst intentan exprimir todavía más la frecuencia de reloj alargando el pipeline a lo bestia, pero el modelo toca techo con consumos y temperaturas desbocados. Este fracaso relativo hace que Intel (y la industria) cambien el chip mental: la carrera de los MHz no tiene recorrido infinito, y entra en escena de forma seria la métrica de rendimiento por vatio.

Forzado por la imposibilidad de llevar NetBurst al mundo portátil y por acuerdos con marcas muy exigentes en diseño como Apple, Intel recicla y mejora la filosofía P6 dando lugar a la familia Core, primero con dobles núcleos derivados de esa arquitectura y luego con una segunda generación radicalmente más eficiente, conocida como Core 2, que vuelve a pegar un salto enorme en IPC frente a Pentium 4.

Estos Core 2 integran por primera vez el Northbridge en el propio procesador y adoptan extensiones a 64 bits compatibles con AMD64, casi doblando el rendimiento por ciclo respecto a generaciones anteriores y marcando uno de los mayores saltos de potencia en la historia de Intel, sólo por detrás del 80286 y el 80486. A partir de ahí, las denominaciones Core i3, i5, i7 (y posteriores i9) se consolidan con arquitecturas como Nehalem, Sandy Bridge, Ivy Bridge, Haswell, Broadwell o Skylake, con mejoras continuas en IPC, caches, controladores de memoria y unidades de predicción de saltos.

Cómo funciona realmente una CPU moderna

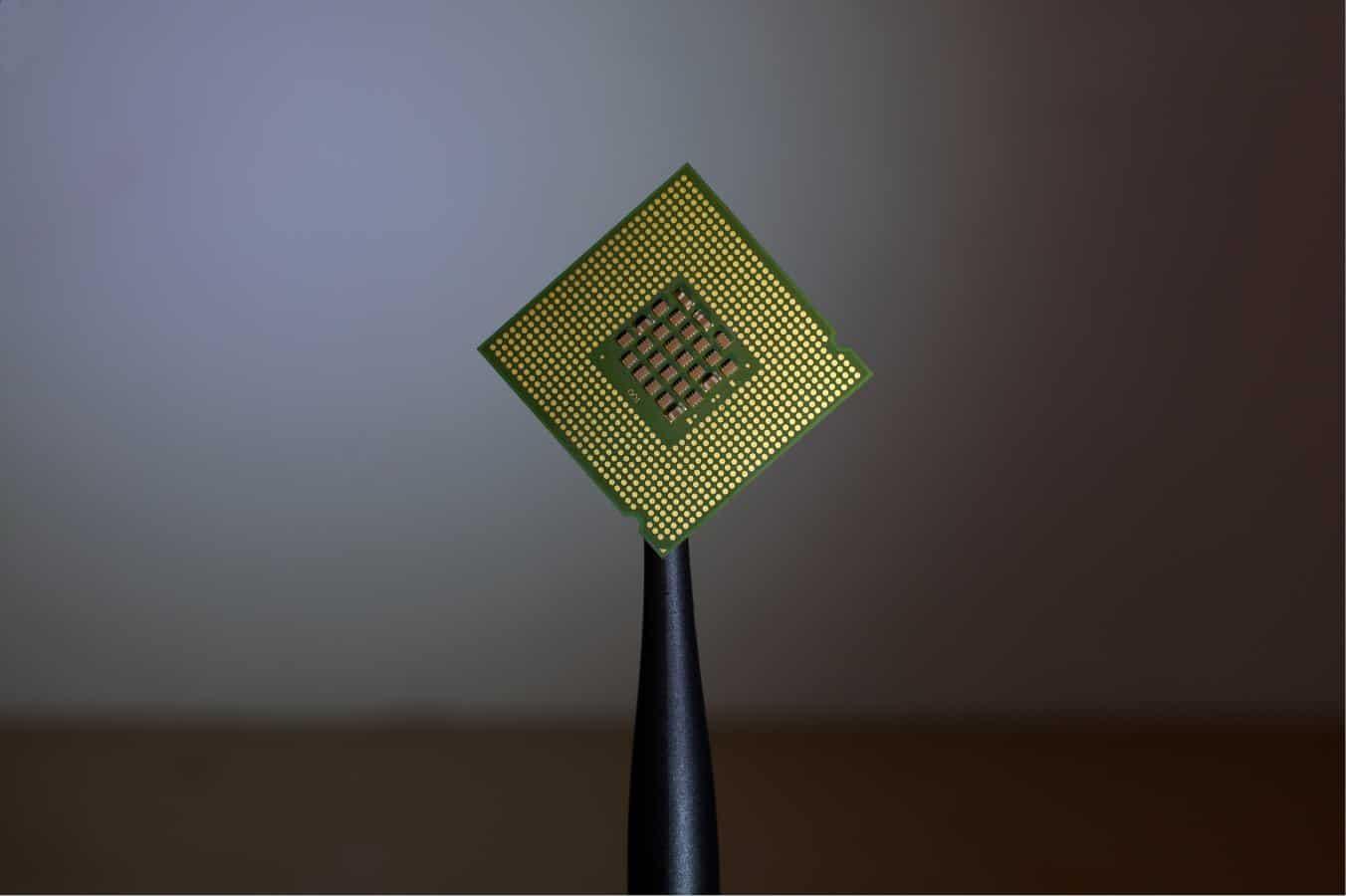

Para entender por qué hemos podido multiplicar la potencia de los procesadores por cientos de miles respecto al Intel 4004, conviene repasar mínimamente qué hay dentro. Una CPU moderna integra en un mismo chip elementos como el encapsulado, unidad de control, ALU, FPU, registros, caches multinivel y puertos de comunicación hacia el resto del sistema.

El encapsulado protege el silicio y facilita la disipación térmica, permitiendo acoplar disipadores y sistemas de refrigeración. La unidad de control (UC) se encarga de organizar y orquestar las instrucciones que llegan desde los programas, decodificarlas y enviarlas a las unidades de ejecución adecuadas en el orden correcto (o desorden correcto, hablando de ejecución out-of-order).

La Unidad Aritmético-Lógica (ALU) realiza operaciones con enteros, mientras que la unidad de coma flotante (FPU) está especializada en cálculos con números reales, fundamentales en gráficas, física y muchas tareas científicas. A esto se suma una pequeña pero rapidísima memoria de registros, donde se guardan datos temporales que la CPU necesita de inmediato.

Entre la CPU y la RAM se sitúan las memorias caché L1, L2 y a menudo L3, cada nivel más grande y algo más lento que el anterior. Su función es reducir la latencia asociada a ir a buscar datos a la RAM, muchísimo más lenta que el núcleo en sí. Una buena jerarquía de caches y una lógica inteligente para predecir qué datos se van a necesitar antes de que hagan falta son claves para exprimir el IPC.

Todo esto funciona en base a una señal de reloj: la CPU envía pulsos eléctricos medidos en Hz (ciclos por segundo), y el número de operaciones que puede completar por unidad de tiempo depende tanto de esa frecuencia como del número de transistores implicados en cada camino crítico. Subir frecuencia normalmente exige subir voltaje, lo que a su vez dispara el calor generado y obliga a sistemas de refrigeración y diseño más complejos.

Los transistores, al final, son pequeños interruptores semiconductores que representan ceros y unos según dejen pasar o no la corriente. Cuanto más pequeños son, más puedes meter en el mismo área de silicio y más trabajo paralelo puedes hacer. De ahí nace la famosa Ley de Moore, formulada por Gordon Moore, cofundador de Intel: aproximadamente cada dos años se duplica el número de transistores en un chip comercial. Aunque ya va bastante forzada, esta observación ha guiado el desarrollo durante más de medio siglo.

Claves de la mejora: miniaturización, arquitecturas y multinúcleo

El grueso de la mejora en rendimiento viene de dos frentes: por un lado, la reducción continua del tamaño de los transistores (el famoso nodo en nanómetros) y, por otro, la optimización de la microarquitectura y el aumento del paralelismo interno.

Al reducir el nodo de fabricación puedes colocar muchos más transistores en la misma superficie, reducir consumos a igual frecuencia y, en general, abrir margen para más núcleos, más caché y unidades de ejecución más anchas. El problema es que según te acercas a tamaños ridículamente pequeños (7 nm, 5 nm y menos), la física se complica: efectos cuánticos, fugas de corriente, sensibilidad extrema a variaciones del proceso… cada salto de nodo se vuelve muchísimo más caro y difícil.

En paralelo, los fabricantes han exprimido la arquitectura interna: pipelines más profundos (o más eficientes), unidades de ejecución más numerosas, mejores predictores de salto, descodificadores más anchos, micro‑op caches para saltarse pasos intermedios, nuevas instrucciones SIMD (MMX, SSE, AVX…) y, sobre todo, el salto a diseños multinúcleo. Meter varios cores dentro del mismo chip permite seguir escalando rendimiento total sin subir tanto la frecuencia.

Hoy un procesador doméstico de gama alta como un Core i7/i9 o un Ryzen puede integrar 6, 8, 12 o más núcleos, cada uno con varios hilos de ejecución, caches compartidas e interconexiones internas optimizadas. Tecnologías como HyperThreading (SMT en terminología genérica) han permitido durante años aprovechar ciclos muertos del pipeline duplicando el número de hilos lógicos por núcleo, con mejoras típicas del 20‑30 % en cargas bien paralelizables.

Sin embargo, en las últimas generaciones Intel está abandonando HyperThreading en algunos diseños en favor de núcleos de eficiencia (E‑Cores) que actúan como “hilos físicos de apoyo” a los núcleos de potencia (P‑Cores). La idea es que estos E‑Cores puedan asumir tareas auxiliares que antes recaían en hilos lógicos, aportando ganancias teóricas superiores al 50 % frente al 30 % clásico del HyperThreading, siempre dependiendo de la carga concreta.

Otro aspecto clave es el aumento de la memoria caché, tanto en tamaño como en velocidad. El salto de 8 a 12 MB de caché L3, por ejemplo, entre procesadores como el i7‑7700 y el i7‑8700, unido a más núcleos y mayor frecuencia turbo, ejemplifica bien cómo se exprimen arquitecturas similares con pequeños ajustes para ofrecer una generación “nueva” de CPU más rápida sin cambiarlo todo desde cero.

AMD, chiplets y el nuevo equilibrio en el mercado

Mientras Intel dominaba a placer el mercado de escritorio y servidores durante años, AMD vivió épocas muy duras, llegando a rozar el abismo hacia 2015. La estrategia de la compañía cambió por completo con apuestas como el modelo fabless (sin fábricas propias), la adopción temprana del diseño con chiplets y una fuerte diversificación hacia GPU, soluciones personalizadas, 5G y aceleradores para centros de datos.

El gran punto de inflexión en CPU llega con Ryzen y la arquitectura Zen. Desde la primera generación Ryzen, y especialmente con la tercera, AMD pasa a fabricar en 7 nm de TSMC mientras Intel sigue atascada en 14 nm para su línea Coffee Lake. No sólo iguala, sino que supera en muchas cargas a los equivalentes de Intel, con mejores consumos y un fuerte empuje en número de núcleos e hilos.

La clave técnica es el uso de chiplets: en lugar de hacer un gran chip monolítico con todos los núcleos y la caché, AMD diseña pequeños bloques repetibles (CCD) conectados a un die de I/O. Esto simplifica la fabricación, mejora el rendimiento de las obleas y permite escalar desde escritorio hasta servidores EPYC con decenas de núcleos simplemente combinando más chiplets dentro del mismo encapsulado.

Sobre esta base, AMD también innova en empaquetado 3D con su 3D V‑Cache, apilando caché L3 sobre los chiplets de CPU para aumentar drásticamente la cantidad de memoria cercana al núcleo, con grandes ventajas en juegos y ciertas cargas sensibles a la latencia. Todo este enfoque está empujando al sector hacia estándares como UCIe (Universal Chiplet Interconnect Express), que en el futuro podrían permitir mezclar chiplets de distintos fabricantes dentro de un mismo paquete.

Gracias a estas apuestas, AMD ha pasado de estar contra las cuerdas a superar a Intel en capitalización bursátil y a competir de tú a tú en prácticamente todos los segmentos: escritorio, portátiles, servidores, consolas y soluciones integradas. Desde dentro de la propia compañía se reconoce que el modelo fabless y las grandes alianzas con foundries han sido cruciales para poder centrarse en diseño, arquitectura e innovación sin cargar con el peso de mantener fábricas punteras.

Procesadores móviles, SoC y el papel de las GPU

Mientras el mundo del PC evolucionaba, en paralelo se estaba gestando otra revolución: la de los SoC móviles basados en ARM. Con el iPhone como detonante mediático y la maduración de Android, el smartphone se convierte en el ordenador más usado del planeta, y con él aparecen procesadores como los Qualcomm Snapdragon, los MediaTek Dimensity, los Exynos de Samsung, los Kirin de Huawei o los Apple A‑series y M‑series.

La Ley de Moore también aplica aquí: se usan nodos muy similares a los de CPU de escritorio, pero con arquitecturas distintas, optimizadas para eficiencia energética extrema y encapsulando en un mismo chip CPU, GPU, módem 4G/5G, controladores de memoria, NPU y otros bloques dedicados. Ese concepto, el System on Chip (SoC), resume la integración total de funciones que en un PC tradicional se reparten en varios chips de la placa.

En el terreno móvil la competencia por el 5G ilustra bien la velocidad de avance: Qualcomm lanza Snapdragon 865 con módem 5G, MediaTek responde con la serie Dimensity 1000 y posteriores como Dimensity 800, y todos compiten por ofrecer más rendimiento con menos consumo y mejor conectividad. En paralelo, las GPUs integradas en estos SoC y las IGP en CPU x86 han ido ganando tanta potencia que para el usuario medio ya no es imprescindible una gráfica dedicada.

Las GPU discretas, eso sí, siguen siendo esenciales en gaming de alto nivel y en computación general sobre GPU (GPGPU). Su arquitectura se basa en cientos o miles de pequeñas unidades de proceso (shaders, stream processors) diseñadas para ejecutar en paralelo masivo operaciones relativamente simples, lo que las hace perfectas para gráficos 3D, entrenamiento de redes neuronales, simulaciones, criptominería y un largo etcétera de tareas altamente paralelizables.

Ejemplos como el minado de Bitcoin usando GPU o el uso de tarjetas gráficas en supercomputadores muestran cómo sacar partido de este tipo de hardware: una CPU generalista coordina, pero son las GPU las que muelen cantidades ingentes de datos con algoritmos paralelos como SHA‑256 o kernels de cálculo científico, alcanzando rendimientos por vatio que una CPU jamás podría igualar en esas cargas.

Por todo ello, el futuro cercano no es CPU vs GPU, sino CPUs con GPUs integradas muy competentes para el usuario general, más GPUs discretas especializadas para juegos, IA y cálculo intensivo, y SoC que combinan todos estos bloques con NPUs dedicadas en un único paquete.

El presente y el futuro: núcleos híbridos, NPU e IA en todas partes

En los últimos años, tanto Intel como AMD y otros actores han empezado a apostar por diseños heterogéneos dentro de la propia CPU. Un ejemplo claro son los Intel Alder Lake y posteriores generaciones, que combinan P‑Cores (núcleos de alto rendimiento) y E‑Cores (núcleos de alta eficiencia) en el mismo die.

El sistema operativo y el hardware colaboran para asignar tareas: los P‑Cores se encargan de cargas pesadas como juegos, render o compilación, mientras que los E‑Cores gestionan tareas de fondo, procesos ligeros o se convierten en “ayudantes” en escenarios donde antes se usaba HyperThreading. Todo esto sucede de forma dinámica, buscando el mejor balance posible entre consumo y rendimiento.

En paralelo, la irrupción de la inteligencia artificial generativa y los asistentes integrados en el sistema operativo (como Copilot+ en Windows 11) está empujando a que las CPU incluyan un tercer tipo de motor: las NPU (Neural Processing Units). Estos bloques dedicados se miden en TOPS (trillones de operaciones por segundo) y están optimizados para multiplicaciones y sumas en matrices, el pan de cada día de las redes neuronales.

Microsoft, por ejemplo, marca como referencia unos 40 TOPS para hablar de un PC de IA Copilot+ “completo”, y fabricantes como Intel con sus Core Ultra 200 o AMD con sus Ryzen AI 300 están ya integrando NPUs que alcanzan potencias de 40‑50 TOPS o más. En sobremesa la NPU convive con la GPU discreta, que seguirá siendo la reina para IA de alto rendimiento, pero en portátiles la presencia de una buena NPU permitirá ejecutar muchas funciones de IA en local sin disparar consumo ni depender de la nube.

Otro frente novedoso es el de la memoria integrada en el propio encapsulado, el llamado Memory on Package (MoP) o soluciones similares a lo que Apple hace con sus SoC M‑series. Intel planea utilizar este enfoque en futuras generaciones de CPU para portátiles, soldando la RAM junto al procesador para reducir latencias y permitir diseños más delgados y ligeros. La desventaja evidente es que ya no se podrá ampliar la RAM sin cambiar todo el paquete CPU+memoria, pero a cambio se ganará en eficiencia y simplicidad de diseño.

Todo esto llega en un contexto donde seguir reduciendo el tamaño del transistor es cada vez más complejo y caro. Ya se fabrican chips en 7 nm, 5 nm e incluso menos, pero la integración masiva en CPU de escritorio y servidores pone al límite la capacidad de las foundries y dispara los costes de las máquinas de litografía y de los propios procesadores. El ritmo de reducción de nodo se ha frenado y la industria está apostando tanto por la miniaturización como por nuevas formas de empaquetado 2D y 3D, chiplets, apilado de memoria y arquitecturas más especializadas.

A largo plazo se sabe que no se puede seguir reduciendo indefinidamente el tamaño de los transistores: un átomo típico ronda los 0,3 nm, y ya estamos en nodos de unos pocos nanómetros efectivos. La barrera atómica marca un fin físico claro al modelo actual. Esto obligará, tarde o temprano, a abrazar otras formas de computación: desde la computación cuántica (todavía muy lejana para uso doméstico) hasta arquitecturas neuromórficas o aceleradores especializados para tareas muy concretas.

Aun así, durante los próximos años todavía veremos mejoras incrementales: ligeras reducciones de nodo con un coste enorme, más chiplets interconectados, más caché apilada en 3D, núcleos heterogéneos más sofisticados y NPUs mucho más potentes y extendidas. El enfoque de empresas como Intel y AMD es claro: centrar buena parte de sus esfuerzos en la IA y en ofrecer procesadores que la integren como algo estándar, no sólo en gamas profesionales, sino también en equipos domésticos y portátiles de consumo.

Mirando todo este recorrido —de los 2.300 transistores del Intel 4004 a los casi 20.000 millones de algunos chips modernos, de los tubos de vacío a las NPUs de 50 TOPS— se ve claro que las CPU han sido y siguen siendo el motor silencioso de la revolución digital. El modelo clásico de “hacer cada vez más pequeño el transistor” está llegando a su límite, pero mientras tanto la industria está sabiendo exprimir arquitecturas, empaquetado e integración de GPU y NPU para seguir ofreciendo más potencia, más eficiencia y nuevas capacidades, con la vista puesta en un futuro donde quizás tengamos que repensar por completo qué entendemos hoy por procesador.